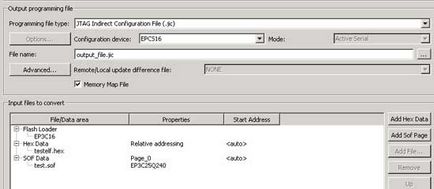

Configurația de tip ROM Altera FEE este programat de interfață JTAG la modul serial activ folosind oricare dintre cablul de descărcare Altera, cum ar fi USB-Blaster, Byte-Blaster și fișierul firmware este utilizat în format de configurare indirect JTAG (.jic). Fișierul Jic poate fi generat din fișierul de configurare .sof FPGA în mediul de proiectare Quartus. Pentru aceasta, efectuați următorii pași:

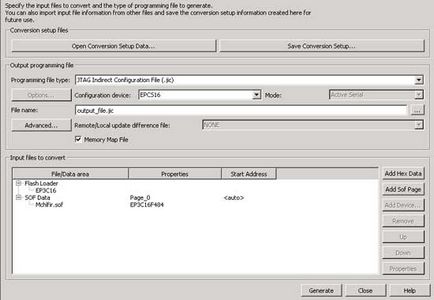

1. În meniul principal File (Fișier)> Convert Files (Programe)

2. Pe panoul rezultat, selectați tipul de fișier programabil ca JTAG Indirect

Fișier de configurare (.jic) din tipul fișierului de programare

3. În câmpul Device configuration, selectați tipul de dispozitiv

4. În câmpul Nume fișier, definiți numele și directorul fișierului .jic de ieșire

5. Faceți clic pe câmpul Date SOF din fișierul Input files to convert

6. Faceți clic pe Adăugare fișier

7. Pentru a extrage un fișier .sof care trebuie convertit în .jic

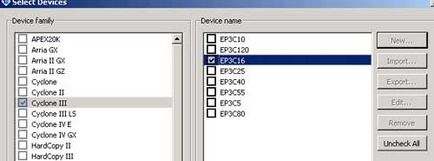

8. Evidențiați câmpul FlashLoader și faceți clic pe butonul Adăugare dispozitiv

9. În panoul care se deschide, selectați dispozitivul FPGA dorit

10. Faceți clic pe butonul Generare

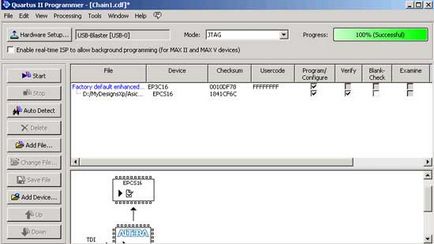

Apoi fișierul .jic pregătit în modul descris mai sus poate fi transferat pe ROM-ul de configurare EPCS în sine folosind programatorul Quartus prin adăugarea unui fișier .jic ca fișier de programare.

Toate procedurile de mai sus sunt descrise într-un document intitulat "Utilizarea FlashLoader-ului serial cu software-ul Quartus II"

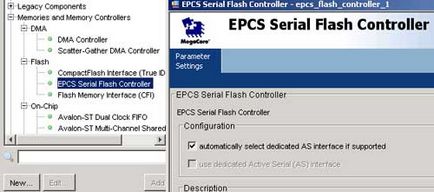

Deci, să creăm și să depanem un proiect cu procesorul Nios II încorporat. Acest lucru va crea două fișiere cu extensii .sof și .elf. Prima este configurația FPGA al doilea program pentru Nios II. Pentru a configura sistemul să funcționeze în mod autonom, este necesar să .elf .sof și au fost plasate în memoria de configurare a reciproc și sunt încărcate în locul potrivit și FPGA On-Chip (SDRAM) pornire. Există mai multe opțiuni pentru această descărcare. Unul dintre ei, în opinia mea cel mai bun loc - sistem de utilizare SOPC FEE Controller-Serial Flash care încorporează un bootloader special - programul pe care se execută de pornire. Încărcătorul (sau încărcătorul de boot) efectuează încărcarea secvențială a componentelor hardware și software ale proiectului și traduce vectorul la începutul programului.

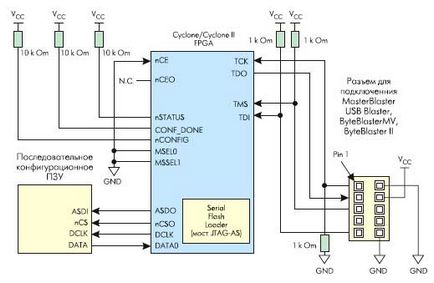

Schema de conectare pentru tipul de dispozitiv Flash de la EPCS la FPGA nu este nimic special. Starea intrărilor Msel [1..0] determină modul de configurare Active Serial.

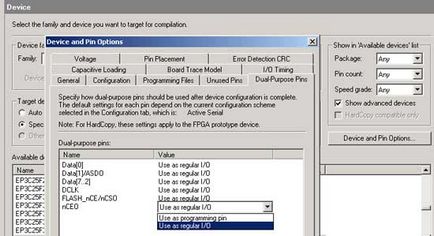

Singurul lucru este că atunci când alocați picioarele, trebuie să instalați toate picioarele scopului dual ca I / O. Pentru aceasta, în meniul Quartus, selectați Asig.> Dispozitiv și faceți clic pe butonul Dispozitiv și Pin. Pe panoul care apare, accesați fila Dual-Purpose Pins și setați toți pinii ca Utilizare ca I / O regulat.

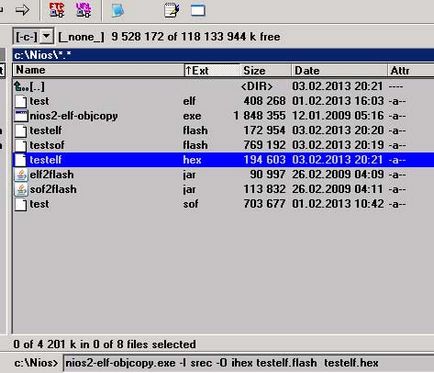

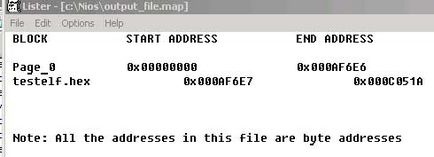

Acum, bazate pe test.sof fișiere și puteți crea testelf.hex imagine .jic - imaginea pentru EPCs flash, care va conține imagini de configurare FPGA și software-ul Nios II consecutiv. După cum este descris la începutul acestei postări, urmați pașii secvențiali pe elementele de la punctul 9. Înainte:

10. Faceți clic pe Add Hex Data și găsiți fișierul de configurare al proiectului test testelf.hex. Specificăm în proprietăți Hex Data Properties - Adresare relativă.

11. Faceți clic pe butonul Generați. După generarea cu succes a fișierului de configurare .jic pentru întregul proiect, acesta poate fi cusut în dispozitivul EPCS folosind programul Quartus

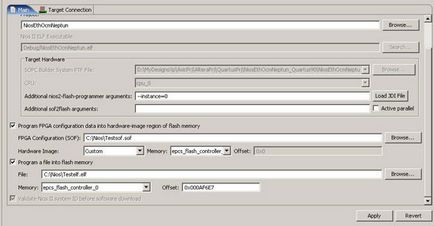

Dacă draga cititor credea că totul, atunci nu. Nu întotdeauna de la versiunea la versiunea Quartus această opțiune funcționează. De exemplu, după pornire, proiectul nu funcționează. Cea mai bună opțiune este programul Nios II Flash Programmer. Cu ajutorul acestuia, puteți bloca imagini ale configurației FPGA și ale programelor Nios II (fișiere .sof și .elf) în dispozitivul EPCS într-o singură lovitură, fără a se încurca în mod special. Cel mai important, o astfel de opțiune este complet operațional, adică pornire modul având în componența sa FPGA (Nios II) + program (de exemplu de operare în SDRAM) pornește și se execută exact ca debugger. Deci, după ce ați studiat Ghidul utilizatorului Nios II Flash Programmer:

Notă: Toate cele de mai sus a fost efectuată pe baza Cuart 9.0 în versiunile ulterioare de programare Cuart FEE produse pentru ajustate tehnologie aceleași caracteristici versiune privată.

Săriți și topiți în rețeaua socială preferată