Generatorul de ceas este compus dintr-un low-pass RC-oscilator, principala unitate de ceas și PLL (PLL). Ea produce următoarele semnale de sincronizare:

- SLCK, semnal de ceas de frecvență joasă, este constantă în cadrul sistemului

- MAINCK randament generator de ceas principal

- PLLCK modul de ieșire PLL și divizor de frecvență

generator de ceas interfață este integrat în consumul de energie controler PMC și este descris în capitolul 26.9. Cu toate acestea, ceasul înregistrează numele sunt combinate în grupul CKGR_.

25.2 joasă frecvență oscilator RC

joasă frecvență oscilator RC - singurul semnal de ceas permanent în cadrul sistemului, inclusiv consumul de energie controler PMC. Acesta este un semnal necesar pentru PMC. Utilizatorul trebuie să ia în considerare posibila oscilator RC de drift. Mai multe informații detaliate sunt prezentate în secțiunea caracteristicile DC.

25.3 ceas master

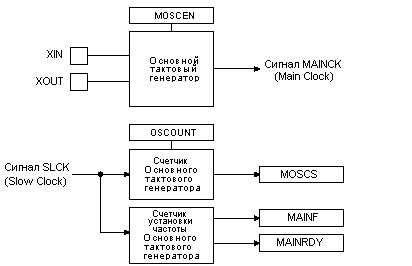

Pe ris.25-1 prezintă o diagramă bloc a generatorului de ceas.

Fig. 25-1. Ceas structural generator de circuit

25.3.1 Activați generatorul principal al ceasului

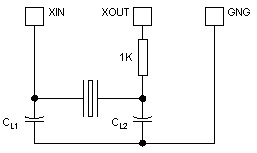

Generatorul de ceas include un oscilator de ceas principal care funcționează cu o frecvență de cristal de 3 până la 20 MHz. Schemă de conexiuni tipică este prezentată în cuarț ris.25-2. Atunci când se lucrează cu cuarț la frecvențe de până la 8 MHz necesită setarea rezistor 1K. Prin terminalele conectate XIN și XOUT condensatoare 25 pF. În consecință, CL1 și rezervor CL2 pot fi omise, folosind cuarț cu intrare egală capacitate 12.5 pF. Mai multe informații detaliate cu privire la caracteristicile electrice prezentate în secțiunea caracteristicile DC.

Fig. 25-2. Un circuit tipic al rezonatorului cuarț

25.3.2 ora începerii generatorului principal al ceasului

începe timpul principal al ceasului într-o anumită secțiune a caracteristicilor DC. timpul de funcționare depinde de frecvența de cuarț și scade odată cu creșterea frecvenței.

25.3.3 de control ceas de bază

Pentru a reduce consumul de energie la pornire a ceasului principal este dezactivat, și este selectat RC oscilator de frecvență joasă.

Software-ul poate activa / dezactiva ceasul principal pentru a reduce consumul de energie. Acest lucru se face prin resetarea MOSCEN biți în registrul generatorului principal (CKGR_MOR).

Decuplarea bit principal de resetare ceas în MOSCEN CKGR_MOR conduce la o resetare automată MOSCS PMC_SR bit în registru care indică faptul că ceasul primar este dezactivat.

Atunci când rezoluția generatorului principal, utilizatorul trebuie să inițializa valoarea contorului a generatorului principal, timpul de pornire corespunzătoare a generatorului. Ora de începere depinde de frecvența de cuarț conectat.

După înregistrarea biți și valorile MOSCEN OSCOUNT în registru pentru a permite CKGR_MOR generatorului principal, MOSCS biți în starea de înregistrare PMC_SR resetare. Contorul începe numărătoarea de la valoarea de pe OSCOUNT descreștere un semnal de frecvență la frecvența de 8 ori a semnalului SLCK. Deoarece valoarea OSCOUNT codificate de 8 biți, atunci timpul maxim de pornire este de aproximativ 62 ms.

În cazul în care contorul ajunge la zero, MOSCS este setat, indicând faptul că frecvența principală oscilator stabilită. Setarea unui bit în MOSCS PMC_IMR poate o sursă de viață de întrerupere microprocesorului.

25.3.4 montare principal contor de frecvență oscilator

frecvența Contor setarea generatorului principal poate determina cu exactitate frecvența oscilator cristal conectat. Acest lucru poate fi util pentru un încărcător program de configurare sticle microcontroler valoarea corectă a semnalului de ceas, indiferent de aplicație.

Contracarării setare principal de frecvență oscilator începe numărătoarea la viteza generatorului de tact după apariția unei muchii pozitive de joasă frecvență oscilator (semnal SLCK) după stabilizarea ceasului principal, adică biții MOSCS odată instalate. Apoi, pe semnalul de margine a 16-bit care se încadrează SLCK MAINRDY este setat în registrul principal CKGR_MCFR Ceas (Registrul frecvență de ceas principal) și contra oprește numărătoarea. Această valoare poate fi citită în registrul MAINF CKGR_MCFR și este egal cu numărul de cicluri ale generatorului de ceas de bază 16 pentru perioade de semnal SLCK. Astfel, frecvența rezonatorului cuarț este conectat poate fi determinată.

25.3.5 Conectarea oscilator extern

ceas extern poate fi conectat în loc de conectare la controlerul de cuarț. În acest caz, semnalul de ceas extern furnizat la terminalul XIN. Xin caracteristicile de ieșire de intrare în aceste condiții sunt prezentate în secțiunea caracteristicile electrice. Programatorul nu ar trebui să uite OSCBYPASS bit setat la 1 și MOSCEN bitul 0 în registrul generatorului principal CKGR_MOR (Main OSC Înregistrare) pentru funcționarea corectă, cu un semnal de ceas extern.

25,4 PLL și divizor de frecvență

PLL incluse în separator de intrare pentru a crește precizia semnalului de ceas rezultat. Cu toate acestea, utilizatorul trebuie să selecteze o valoare minimă a frecvenței la divizorul de intrare PLL în timpul de programare.

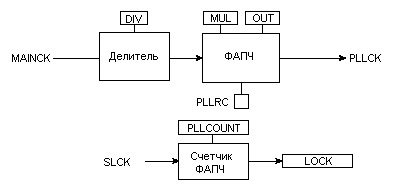

Pe ris.25-3. prezintă o diagramă bloc a unui PLL și divizorul de frecvență.

Fig. 25-3. Schema bloc a PLL și divizor de frecvență

25.4.1 filtru PLL

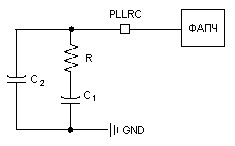

PLL necesită conectarea unui filtru extern de ordinul 2 prin PLLRC portul. Pe ris.25-4 prezintă un astfel de circuit de filtrare.

Fig. 25-4. Schema de filtru PLL

Valorile nominale R, C1 și C2, conectat la concluzia PLLRC, calculată în funcție de frecvența de intrare a PLL, frecvența de ieșire PLL și faza. Selectarea valorilor optime se realizează prin semnalul de ieșire de deplasare și ora de începere.

25.4.2 Programarea PLL și frecvența compas

Divizorul poate fi setat în intervalul de la 1 la 255. Când înregistrați în DIV divizor zero la ieșirile divizor respective și PLL este setat un semnal de nivel scăzut. După reset, în fiecare domeniu este înregistrat DIV zero, ceea ce conduce la o reglare la zero la intrările de ceas respective ale PLL.

PLL permite semnalelor de ieșire de multiplicare de separatoare. Frecvența semnalului de ceas PLL depinde de frecvența semnalului original și parametrii DIV și MUL. Valoarea frecvenței de ieșire este determinată prin expresia (MUL + 1) / DIV. Scrierea în MUL zero, dezactivează PLL. Includerea circuitului PLL este în valoarea MUL înregistrare mai mare decât zero.

După trecerea Reglaj sau a schimba unul dintre parametrii săi LOCK bit în registrul este resetat automat PMC_SR. Valorile înregistrate în PLLCOUNT registru câmp CKGR_PLLR sunt încărcate în contorul PLL. Contor PLL apoi decrementat de SLCK semnal de viteză pentru a ajunge la zero. În acest moment PMC_SR LOCK bit în registru este setat și poate genera o întrerupere a procesorului. Utilizatorul trebuie să descarce numărul SLCK de cicluri de semnal în câmpul PLLCOUNT care determină suprapunerea procesului de tranziție a PLL. Durata procesului tranzitoriu depinde de filtru PLL. Parametrii inițiali și frecvența de ieșire PLL poate fi calculată cu ajutorul unui instrument special oferit de Atmel.